# super-QR/PSR<sup>™</sup> CV/CC Controller

#### **FEATURES**

- **♦** Easily Meet EPS Level 6

- ♦ Less than 75mW Standby Power

- ◆ Proprietary super-QR/PSR<sup>™</sup> (Quasi-Resonant & Primary Side Regulation) Control for High Efficiency and Low EMI

- ♦ ±5% CC and CV Precision

- **♦** Proprietary Cable Drop Compensation

- **♦** Smart Output Short Protection

- **♦** Cycle-by-Cycle Current Limiting

- ◆ Built-in Leading Edge Blanking (LEB)

- ♦ Pin Floating Protection

- ♦ Built-in Soft Start

- Output Over Voltage Protection

- ♦ VDD OVP & Clamp

- VDD Under Voltage Lockout (UVLO)

#### **APPLICATIONS**

- Battery chargers for cellular phones, cordless phones, PDA, digital cameras, etc

- **♦** Replaces linear transformer and RCC SMPS

- ◆ AC/DC LED lighting

#### **GENERAL DESCRIPTION**

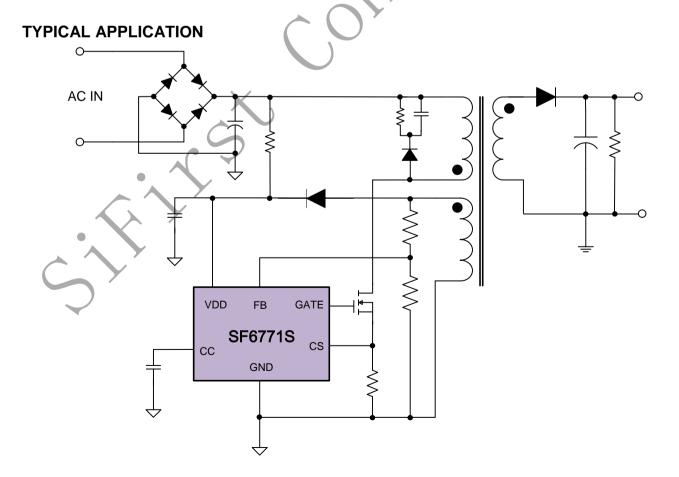

SF6771S is a high performance, highly integrated QR (Quasi Resonant Mode) and Primary Side Regulation (PSR) controller for offline small power converter applications.

SF6771S has proprietary *super-QR/PSR<sup>TM</sup>* control for high efficiency and low EMI. The standby power is less than 75mW @230VAC. Thus, the IC can meet EPS Level 6 energy standard easily. The IC also has built-in cable drop compensation function, which can provide excellent CV performance.

SF6771S integrates functions and protections of Under Voltage Lockout (UVLO), VDD Over Voltage Protection (VDD OVP), Soft Start, Cycle-by-cycle Current Limiting (OCP), Pin Floating Protection, Gate Clamping, VDD Clamping.

SF6771S is available in SOT23-6 package.

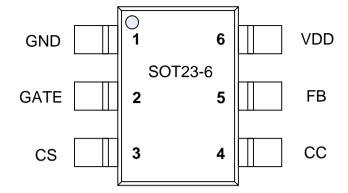

# **Pin Configuration**

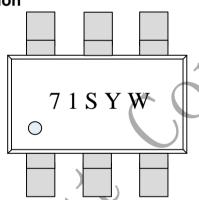

**Ordering Information**

| Part Number | Top Mark | Pacl    | Tape & Reel |     |

|-------------|----------|---------|-------------|-----|

| SF6771SLGT  | .71SYW   | SOT23-6 | Green       | Yes |

# **Marking Information**

Dot: Pin1 Mark 71S:Part number SF6771S YW: Year&Week Code

# Pin Description

| Pin Num | Pin Name | Ī/O | Description                                                                                                                                                               |

|---------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Р   | Ground                                                                                                                                                                    |

| 2       | GATE     | 0   | Totem-pole gate driver output to drive the external MOSFET.                                                                                                               |

| 3       | CS       |     | Current sense pin.                                                                                                                                                        |

| 4       | CC       | 0   | Connect a capacitor between this pin and GND for CC regulation.                                                                                                           |

| 5       | FB       | I   | System feedback pin. This control input regulates both the output voltage in CV mode and output current in CC mode based on the flyback voltage of the auxiliary winding. |

| 6       | VDD      | Р   | IC power supply pin.                                                                                                                                                      |

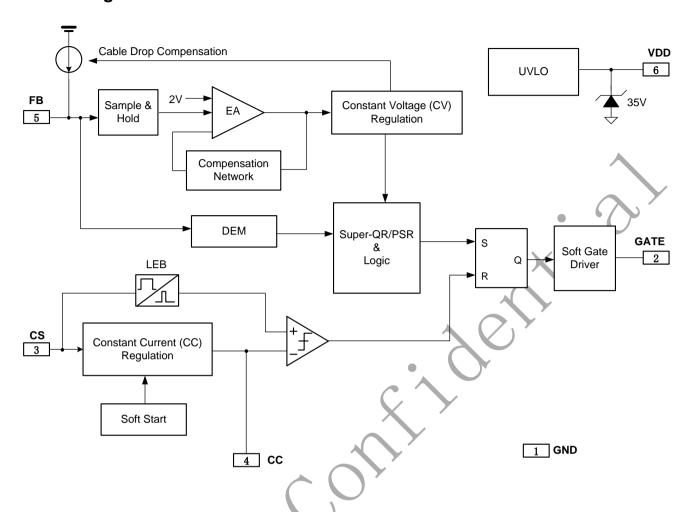

# **Block Diagram**

Absolute Maximum Ratings (Note 1)

| Parameter                              | Value      | Unit |

|----------------------------------------|------------|------|

| VDD DC Supply Voltage                  | 35         | V    |

| VDD DC Clamp Current                   | 10         | mA   |

| GATE pin                               | 20         | V    |

| CC, CS voltage range                   | -0.3 to 7  | V    |

| FB voltage range                       | -0.7 to 7  | V    |

| Package Thermal Resistance (SOT-26)    | 250        | °C/W |

| Maximum Junction Temperature           | 150        | °C   |

| Operating Temperature Range            | -40 to 85  | °C   |

| Storage Temperature Range              | -65 to 150 | °C   |

| Lead Temperature (Soldering, 10sec.)   | 260        | °C   |

| ESD Capability, HBM (Human Body Model) | 3          | kV   |

| ESD Capability, MM (Machine Model)     | 250        | V    |

Recommended Operation Conditions (Note 2)

| 1100011111011000 Oporation Conditions (110to 2) |           |      |  |  |  |  |

|-------------------------------------------------|-----------|------|--|--|--|--|

| Parameter                                       | Value     | Unit |  |  |  |  |

| Supply Voltage, VDD                             | 10 to 30  | V    |  |  |  |  |

| Operating Ambient Temperature                   | -40 to 85 | °C   |  |  |  |  |

| Maximum Switching Frequency                     | 120K      | Hz   |  |  |  |  |

## **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = 25<sup>o</sup>C, VDD=16V, if not otherwise noted)

| Symbol                                      | Parameter                         | Test Conditions            | Min  | Тур  | Max  | Unit   |

|---------------------------------------------|-----------------------------------|----------------------------|------|------|------|--------|

| Supply Voltag                               | ge (VDD) Section                  |                            |      |      |      |        |

| I_Startup                                   | VDD Start up Current              | VDD =UVLO(ON)-1V,          |      | 2    | 20   | uA     |

|                                             |                                   | Measure current into VDD   |      |      |      |        |

| I_VDD_Op                                    | Operation Current                 | $V_{FB}=1V,CL=0.5nF,$      |      | 1    | 1.5  | mA     |

|                                             |                                   | VDD=20V                    |      |      |      |        |

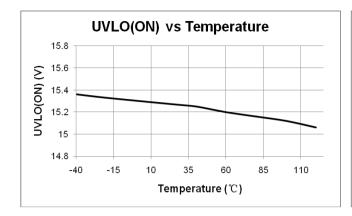

| UVLO(ON)                                    | VDD Under Voltage                 |                            | 14   | 15.5 | 16.5 | V      |

|                                             | Lockout Exit (Startup)            |                            |      |      |      |        |

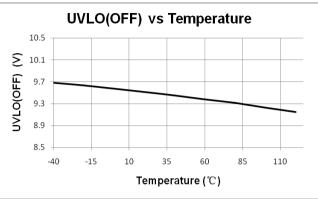

| UVLO(OFF)                                   | VDD Under Voltage                 |                            | 8.5  | 9.5  | 10.5 | V      |

| \ (D.D. \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Lockout Enter                     |                            |      |      |      | 11     |

| VDD_OVP                                     | VDD Over Voltage                  |                            | 31   | 33   | 35   | V      |

| \/ Ol                                       | Protection trigger                | 10/                        | 00   | 0.5  | 07   |        |

| V <sub>DD</sub> _Clamp                      | VDD Zener Clamp                   | $I(V_{DD}) = 7 \text{ mA}$ | 33   | 35   | 37   | V      |

| Faadbaak lee                                | Voltage                           |                            |      |      |      |        |

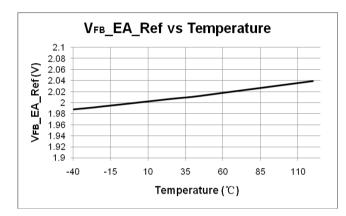

|                                             | ut Section(FB Pin) Internal Error | T                          | 1.07 | 2.0  | 2.03 | V      |

| V <sub>FB</sub> _EA_Ref                     |                                   |                            | 1.97 | 2.0  | 2.03 | V      |

|                                             | Amplifier(EA) reference input     |                            |      |      |      |        |

| V <sub>FB</sub> _Short                      | Output Short Circuit              |                            |      | 1.35 |      | V      |

| V <sub>FB</sub> _SHOIL                      | Threshold                         |                            |      | 1.33 |      | V      |

| T <sub>FB</sub> _Short                      | Output Short Circuit              | Y                          |      | 18   |      | mSec   |

| TFB_OHOT                                    | Debounce Time                     |                            |      | 10   |      | 111000 |

| V <sub>FB</sub> _DEM                        | Demagnetization                   |                            |      | 75   |      | mV     |

| VPD_D =                                     | comparator threshold              | $\sim$                     | ,    |      |      | 1      |

| T <sub>min</sub> _OFF                       | Minimum OFF time                  | V Y                        |      | 2    |      | uSec   |

|                                             |                                   |                            |      |      |      |        |

| T <sub>max</sub> OFF                        | Maximum OFF time                  | <b>*</b>                   |      | 3    |      | mSec   |

| I <sub>Cable</sub> _max                     | Max Cable                         |                            |      | 55   |      | uA     |

| Cable_IIIQX                                 | compensation current              | <b>()</b>                  |      |      |      |        |

| Current Sense                               | e Input Section (CS Pin)          |                            | · I  | · L  | _L   | 1      |

| T_blanking                                  | CS Input Leading                  |                            |      | 500  |      | nSec   |

| _* 3                                        | Edge Blanking Time                |                            |      |      |      |        |

| T <sub>D</sub> OC                           | Over Current                      | CL=0.5nF at GATE,          |      | 100  |      | nSec   |

|                                             | Detection and Control             |                            |      |      |      |        |

|                                             | Delay                             |                            |      |      |      |        |

| Constant Curi                               | rent Section (CC Pin)             |                            |      |      |      | 1      |

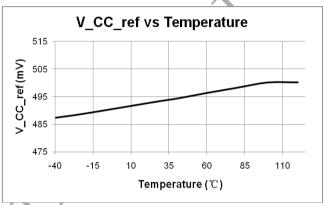

| V_CC_ref                                    | Internal CC reference             |                            | 490  | 500  | 510  | mV     |

|                                             |                                   |                            | 100  | 000  | 0.10 | 111 V  |

| Gate Drive Ou                               | itput                             |                            |      |      |      |        |

| VOL                                         | Output Low Level                  | lo = 20 mA (sink)          |      |      | 1    | V      |

| VOH                                         | Output High Level                 | lo = 20 mA (source)        | 7.5  |      |      | V      |

| VG_Clamp                                    | Output Clamp Voltage              | VDD=24V                    |      | 16   |      | V      |

|                                             | Level                             |                            |      |      |      |        |

| T_fr                                        | Output Rising Time                | CL = 0.5nF                 |      | 700  |      | nSec   |

| T                                           | Output Falling Time               | CL =0.5nF                  |      | 35   |      | nSec   |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2.** The device is not guaranteed to function outside its operating conditions.

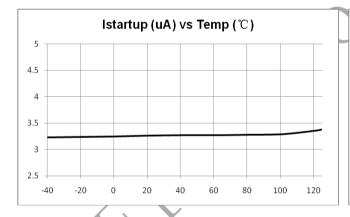

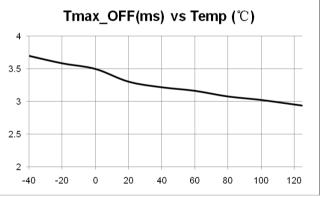

# **CHARACTERIZATION PLOTS**

## **OPERATION DESCRIPTION**

SF6771S is a high performance, multi mode controlled, highly integrated QR (Quasi Resonant) Primary Side Regulation (PSR) controller. The built-in high precision CV/CC control with high level protection features make it very suitable for offline small power converter applications.

### **♦** Startup Current and Startup Control

Startup current of SF6771S is designed to be very low (typically 2uA) so that VDD could be charged up above UVLO(ON) threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet reliable startup in application.

### **♦** Operating Current

The operating current in SF6771S is as small as 1mA (typical). The small operating current results in higher efficiency and reduces the VDD hold-up capacitance requirement..

# ◆ super-QR/PSR<sup>™</sup> Control

SF6771S uses a proprietary *super-QR/PSR<sup>TM</sup>* control for high efficiency and low EMI. The IC works in Quasi-Resonant (QR) mode in Constant Current (CC) and Constant Voltage (CV) mode. In this way, the efficiency is boosted and the EMI is reduced greatly. The IC can easily meet EPS level 6 standard.

### **♦** Constant Current (CC) Regulation

SF6771S can accurately control the output current by the internal current feedback control loop. The output mean current in constant current (CC) mode can be approximately expressed as:

$$I_{CC}(mA) = \frac{N}{2} \times \frac{500(mV)}{Rcs(\Omega)}$$

In the equation above,

N----The turn ratio of primary side winding to secondary side winding.

Rcs--- the sensing resistor connected between the MOSFET source to GND.

### ◆ Precision CV/CC Performance

In SF6771S, the parameters are trimmed to tight range, which makes the system CC/CV to have less than 5% variation.

#### **♦** Soft Start

SF6771S features an internal soft start that slowly increases the threshold of cycle-by-cycle current limiting comparator during startup sequence. It reduces the stress on the secondary diode during startup. Every startup process is followed by a soft start activation.

# Proprietary Cable Voltage Drop Compensation in CV Mode

When it comes to cellular phone charger applications, the battery is located at the end of cable, which causes typically several percentage of voltage drop on the actual battery voltage. SF6771S has a proprietary built-in cable voltage drop compensation block which can provide a constant output voltage at the end of the cable over the entire load range in CV mode.

# **♦** Leading Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs across the sensing resistor. To avoid premature termination of the switching pulse, an internal leading edge blanking circuit is built in. During this blanking period (500ns, typical), the cycle-by-cycle current limiting comparator is disabled and cannot switch off the gate driver. Thus, external RC filter with a small time constant is enough for current sensing.

### **♦** Minimum and Maximum OFF Time

In SF6771S, a minimum OFF time (typically 2us) is implemented to suppress ringing when GATE is off. The minimum OFF time is necessary in applications where the transformer has a large leakage inductance, particularly at low output voltages or startup. The maximum OFF time in SF6771S is typically 3ms, which provides a large range for frequency reduction. In this way, a low standby power of 70mW can be achieved.

#### **♦** Smart Output Short Protection

The output short circuit protection of conventional PSR system is based on the coupling between auxiliary winding and secondary winding. When output is short, the auxiliary winding cannot provide enough energy to the IC any more. In this way, the system will enter into auto-recovery mode protection. However, the IC may be wrongly supplied if the leakage inductance of the primary winding is large enough.

In SF6771S, if output short circuit occurs, the IC will detect the situation and enter into auto-recovery mode protection.

## ◆ VDD OVP(Over Voltage Protection)

VDD OVP (Over Voltage Protection) is implemented in SF6771S and it is a protection of auto-recovery mode.

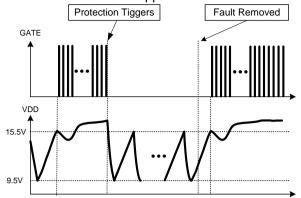

### **♦** Auto Recovery Mode Protection

As shown in Fig.1, once a fault condition is detected, switching will stop. This will cause VDD to fall because no power is delivered form the auxiliary winding. When VDD falls to UVLO(off) (typical 9.5V), the protection is reset and the operating current reduces to the startup current, which causes VDD to rise, as shown in Fig.1. However, if the fault still exists, the system will experience the above mentioned process. If the

fault has gone, the system resumes normal operation. In this manner, the auto restart can alternatively enable and disable the switching until the fault condition is disappeared.

Fig.1

# **♦** Pin Floating Protection

In SF6771S, if pin floating situation occurs, the IC is designed to have no damage to system.

### **♦** Soft Gate Drive

SF6771S has a soft totem-pole gate driver with optimized EMI performance. An internal 16V clamp is added for MOSFET gate protection at higher than expected VDD input.

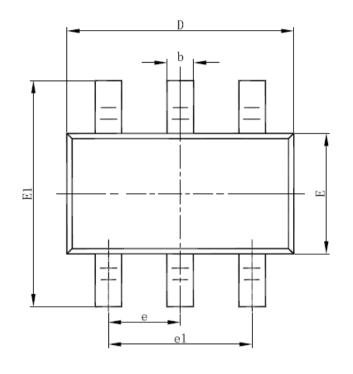

# **PACKAGE MECHANICAL DATA**

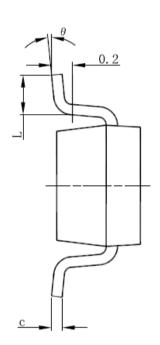

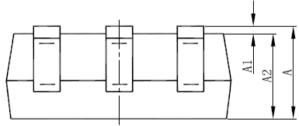

# SOT-23-6L PACKAGE OUTLINE DIMENSIONS

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| Α      | 1.000        | 1.300         | 0.039                | 0.051 |  |

| A1     | 0.000        | 0.150         | 0.000                | 0.006 |  |

| A2     | 1.000        | 1.200         | 0.039                | 0.047 |  |

| b      | 0.300        | 0.500         | 0.012                | 0.020 |  |

| С      | 0.100        | 0.200         | 0.004                | 0.008 |  |

| D'     | 2.800        | 3.020         | 0.110                | 0.119 |  |

| UE)    | 1.500        | 1.700         | 0.059                | 0.067 |  |

| E1     | 2.600        | 3.000         | 0.102                | 0.118 |  |

| e      | 0.950        | (BSC)         | 0.037 (BSC)          |       |  |

| e1     | 1.800        | 2.000         | 0.071                | 0.079 |  |

| Ĺ      | 0.300        | 0.600         | 0.012                | 0.024 |  |

| θ      | O°           | 8º            | 00                   | 80    |  |

#### IMPORTANT NOTICE

SiFirst Technology Nanhai, Ltd (SiFirst) reserves the right to make corrections, modifications, enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

SiFirst warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with SiFirst's standard warranty. Testing and other quality control techniques are used to the extent SiFirst deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

SiFirst assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using SiFirst's components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

Reproduction of SiFirst's information in SiFirst's data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. SiFirst is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of SiFirst's products or services with statements different from or beyond the parameters stated by SiFirst for that product or service voids all express and any implied warranties for the associated SiFirst's product or service and is an unfair and deceptive business practice. SiFirst is not responsible or liable for any such statements.

SiFirst's products are neither designed nor intended for use in military applications. SiFirst will not be held liable for any damages or claims resulting from the use of its products in military applications.

SiFirst's products are not designed to be used as components in devices intended to support or sustain human life. SiFirst will not be held liable for any damages or claims resulting from the use of its products in medical applications.